# **Advantech AE Technical Share Document**

| Date             | 2022 / 01 / 05                                            | Related    | CODECAC              | CODEGVE      |  |  |

|------------------|-----------------------------------------------------------|------------|----------------------|--------------|--|--|

| Category         | ■ FAQ □ SOP                                               | Product    | CODESTS              | CODESYS      |  |  |

| Abstract         | IAG_FAQ_CODESYS_EtherCAT_Diagnosis                        |            |                      |              |  |  |

| Keyword          | EtherCAT · RX error count · CRC Error · Link Lost Counter |            |                      |              |  |  |

| SR#              | 1-4753217541                                              |            |                      |              |  |  |

| Revision History |                                                           |            |                      |              |  |  |

| Date             | Version                                                   | Author     | Reviewer Description |              |  |  |

| 2022 / 01 / 14   | V1.0                                                      | Tenjin.Lin | Owen.chang           | CODESYS SP16 |  |  |

|                  |                                                           |            |                      |              |  |  |

|                  |                                                           |            |                      |              |  |  |

### **■** Problem Description & Architecture:

This article will focus on the errors and diagnostic guidelines that occur in the EtherCAT hardware layer. You can use various phenomena such as Invalid frame, Link Lost Counter, and Forwarded CRC Error to determine the problems that occur, and explain how to catch related errors.

## ■ Brief Solution - Step by Step:

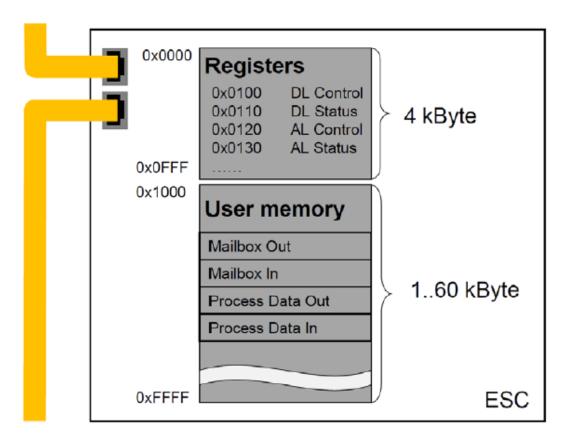

The ESC address space of a slave is divided into two parts:

Register area  $[0x0000 \sim 0x0FFF]$ : settings of the data link layer, commands and diagnostic counters, this article mainly describes the diagnostic counters.

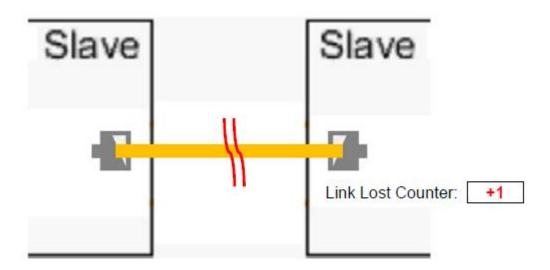

First, it is stated that the increase in the value of the link loss counter reflects the interruption of the hardware communication channel - the data frame on this link is not sent to the neighboring device:

Most links are lost because of the following:

- Temporary or permanent device power outage, or device reboot

- Damaged cables, connectors, or poor quality connectors

- EMC

When the physical connection on a port is interrupted, the slave station will increase the LinkLostCounter (connection loss counter) of the port by 1

| Register | Length | Meaning                  | Cleared by                                     |  |

|----------|--------|--------------------------|------------------------------------------------|--|

| 0x0310   | 1 byte | Lost Link Counter port 0 | Writing any of these registers from the master |  |

| 0x0311   | 1 byte | Lost Link Counter port 1 |                                                |  |

| 0x0312   | 1 byte | Lost Link Counter port 2 |                                                |  |

| 0x0313   | 1 byte | Lost Link Counter port 3 |                                                |  |

This counter is reset when the ESC is powered on or when the master writes a value to one or more link loss counters 0X0310-0X0313.

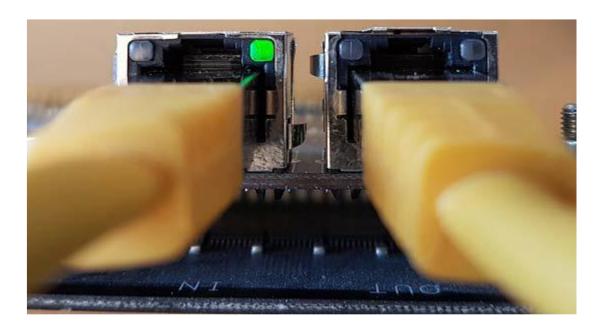

EtherCAT slave devices mandate that each pluggable port supports link/run lights.

The reason for the permanent interruption of the connection may be that the connector has been pulled out, the cable is badly damaged, or the device has lost power.

#### Error determination method:

- 1. Before checking the link loss counter (or for some slaves that do not support the link loss counter), It is easy to see if there is a permanent link loss problem by looking at the link/run light: in this case the LED will be always off state

- 2. The count on the link loss counter indicates that there is a disconnection at the physical layer, and the link loss counter only counts when the port is OPEN.

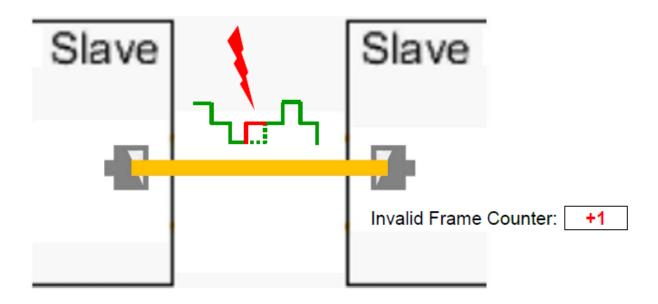

Next explain Invalid frame, which is a combination of CRC Error Counter and RX Error Counter. The meaning of Invalid frame is that the hardware signal reaches the neighboring slave station but the received signal is inconsistent with the original sent.

There are two main factors for this problem:

- 1. External EMC interference (usually the counter increases from time to time)

- 2. Equipment or interface damage (usually accompanied by high-speed and systematic counter value growth)

Both the RX error counter and the CRC check error counter indicate corruption of the data frame received by the hardware, their meanings are very similar, but their meanings are slightly different due to how they are verified.

| Register | Length | Meaning                  |                              |  |

|----------|--------|--------------------------|------------------------------|--|

| 0x0300   | 1 byte | CRC Error Counter port 0 | Invalid Frame Counter port 0 |  |

| 0x0301   | 1 byte | RX Error Counter port 0  |                              |  |

| 0x0302   | 1 byte | CRC Error Counter port 1 | Invalid Frame Counter port 1 |  |

| 0x0303   | 1 byte | RX Error Counter port 1  |                              |  |

| 0x0304   | 1 byte | CRC Error Counter port 2 | Invalid Frame Counter port 2 |  |

| 0x0305   | 1 byte | RX Error Counter port 2  |                              |  |

| 0x0306   | 1 byte | CRC Error Counter port 3 | Invalid Frame Counter port 3 |  |

| 0x0307   | 1 byte | RX Error Counter port 3  |                              |  |

Invalid Frame Counters report the following compound information:

- RX Errors (counted by RX Error Counters):

- Correspond to individual invalid symbols

- Can occur both within and outside frames (when occurring within frames , they represent usually also CRC Errors)

- CRC Errors(counted by CRC Error Counters):

- Correspond to frames whose overall bit sequence was corrupted

- Can occur only within frames

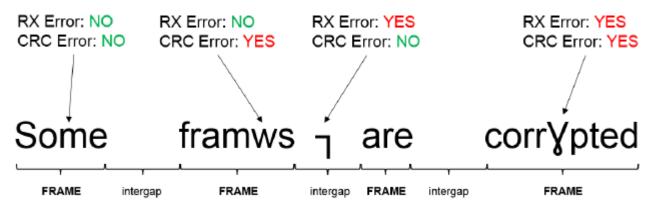

The difference between the two error types can be explained taking a written language as comparison:

#### Error determination method:

- 1. Therefore, for EMC interference, it can be judged by the way that both RX and CRC errors increase at the same time. (Even though the increased probability of the two may be different), because external interference cannot be synchronized with the communication, it will cause damage both inside and outside the Ethernet data frame.

- 2. If the count value when RX and CRC are completely unbalanced (many RX errors but no CRC errors, or very CRC errors and no RX errors) may represent an internal hardware error of one of the slaves.

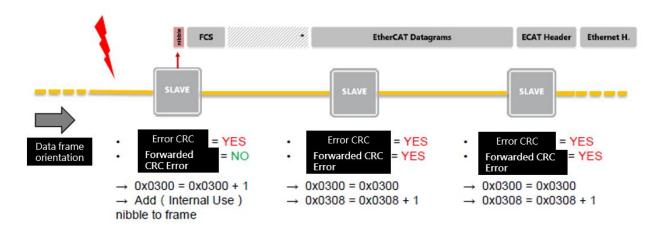

Next explain Besides Frame Error Counters, some ESCs support also an error forwarding mechanism and associated Previous Error Counters (Forwarded CRC Error Counters):

| 0x0308 | 1 byte | Forwarded RX Error Counter port 0 |

|--------|--------|-----------------------------------|

| 0x0309 | 1 byte | Forwarded RX Error Counter port 1 |

| 0x030A | 1 byte | Forwarded RX Error Counter port 2 |

| 0x030B | 1 byte | Forwarded RX Error Counter port 3 |

When such an ESC detects an error for the first time, an FCS check error and an extra data bit are appended to the end of the data frame that will be forwarded to the next slave. The frame will be checked by the next slave (according to the PHY/ESC used on both sides) and the error will be mapped into the corresponding forwarding error counter register

Its operating principle is that the first slave station that detects a CRC error increases its CRC error counter (Register0x0300), and the second and subsequent slave stations that check for a CRC error increase its forwarding CRC error counter (Register0x0308)while the CRC error counter remains unchanged.

#### Error determination method:

- 1. The operation mechanism of Forwarded CRC error can be used to determine the location of the error point. For example, when an ESC port significantly increases the Forwarded CRC counter, but the RX and Invalid Frame error counters do not change significantly. At this point, the problem is not on this ESC port.

- 2. Not all slaves support the Forwarded CRC Error Counters function (this feature is optional), so this count should be considered as supplementary information: useful for locating the 1st device in error, but not a key indicator.

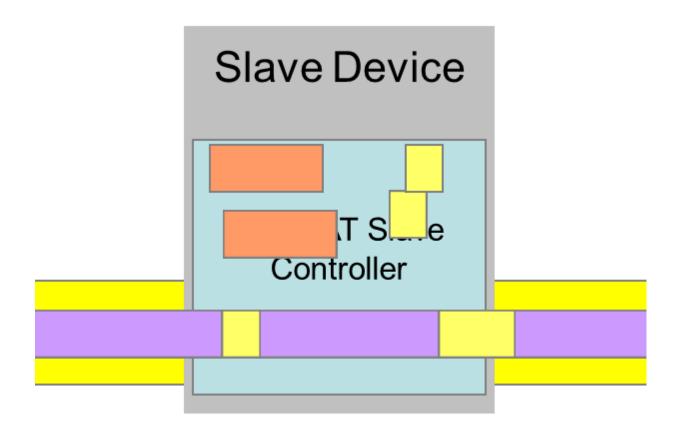

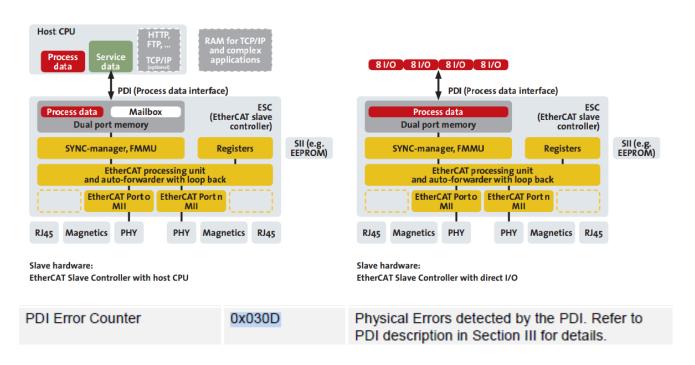

The EtherCAT Processing Unit reads and/or writes data from/to EtherCAT frames "on-the-fly" (no store-and-forward in the Slave)

Here, the ECAT Processing Unit Error Counter is used to detect FCS errors or datagram structure errors.

| 0x030C 1 byte | EtherCAT Processing Unit Error<br>Counter | Writing register<br>0x030C from master |

|---------------|-------------------------------------------|----------------------------------------|

|---------------|-------------------------------------------|----------------------------------------|

PDI is used to connect between applications and ESCs, where PDI has several types: digital I / O, SPI from SPI slave, 8-16-bit microcontroller, on-chip bus, multi-function I / O. PDI Error Counter indicates a count of errors in these interfaces.

| Bit | Description                                                                                                  | ECAT         | PDI | Reset Value |

|-----|--------------------------------------------------------------------------------------------------------------|--------------|-----|-------------|

| 7:0 | PDI Error counter (counting is stopped when 0xFF is reached). Counts if a PDI access has an interface error. | r/<br>w(clr) | r/- | 0           |

|     |                                                                                                              |              |     |             |

| Bit | Description                                                                                                  | ECAT         | PDI | Reset Value |

|     | Reasons for last PDI Error                                                                                   | r/-          | r/- | 0           |

| 2:0 | Number of SPI clock cycles of whole access (modulo 8) causing PDI Error                                      |              |     |             |

| 3   | Busy violation during read access: 0: no error 1: error detected                                             |              |     |             |

| 4   | Read termination missing: 0: no error 1: error detected                                                      |              |     |             |

| 5   | Access continued after read termination byte 0: no error 1: error detected                                   |              |     |             |

| 7:6 | SPI command CMD[2:1] of access causing PDI Error.                                                            |              |     |             |

If there is an error in the PDI Error Counter, you can read 0X30E to know the error content. But mainly PDI error and Processing Unit are not very helpful for judging the problem of Slave.

## **■** Reference:

EtherCAT\_Diagnosis\_For\_Users

EtherCAT\_Diagnosis\_For\_Developers

TwinCAT 控制系统中 EtherCAT 诊断和错误查找

LAN9252

Hardware Data Sheet Section

CODESYS Online Help