# SOM-ETX Series System On Modules

# **Design Guide**

Version 1.2

#### Notices

The copyright on this user manual remains with Advantech Co., Ltd. No part of this user manual may be transmitted, reproduced, or changed.

Other companies' product names that may be used herein remain the property of their respective owners.

The product specifications, design and this user's manuals content are subject to change without notice.

If you have any questions, please contact your merchant or our service center for clarification. We are not responsible for any losses resulting from using this product no matter what the reason.

## **Revision History**

| Version/Revision date | Date           | Description                                                                |

|-----------------------|----------------|----------------------------------------------------------------------------|

| Version 1.0           | May 29, 2005   | Initial release                                                            |

| Version 1.1           | April 28, 2006 | Revision No.1                                                              |

| Version 1.2           | Sep 17, 2010   | Remove SOM-ETX model name<br>and let it become a standard<br>design guide. |

|                       |                |                                                                            |

Part No: 20060ETX00

## **Table of Contents**

|      | 1.1        | Term    | ninology                                                   |     |

|------|------------|---------|------------------------------------------------------------|-----|

|      |            |         | Table 1.1 Conventions and Terminology                      |     |

|      | 1.2        | Refe    | renced Documents                                           |     |

|      | ~ .        | •       | Table 1.2 Referenced Documents                             |     |

| . 4  | 2.1        |         | view                                                       |     |

|      |            | Interfa | ce I/O Voltage                                             |     |

|      |            |         | Table 2.53 DC Specifications for 5V Signaling of PCI Bus   |     |

|      |            |         | Table 2.54 DC Specifications for 3.3V Signaling of PCI Bus |     |

|      |            |         | Table 2.55 DC Specification of USB Signals                 |     |

|      |            |         | Table 2.56 AC'97 CODEC DC Specifications                   |     |

|      |            |         | Table 2.57 AC'97 CODEC Analog I/O DC Specifications        |     |

|      |            |         | Table 2.58 Hsync and Vsync Signals Specifications          |     |

|      |            |         | Table 2.59 RGB Voltage                                     | .13 |

|      |            |         | Table 2.60 LCD I/O Voltage                                 | .13 |

|      |            |         | Table 2.61 Ultra DMA modes 1-4 (5V)                        | .14 |

|      |            |         | Table 2.62 Ultra DMA modes 5 (3.3V)                        | .14 |

|      |            |         | Table 2.63 Ethernet I/O Voltage                            | .14 |

|      |            |         | Table 2.64 TV-Out I/O Voltage                              | .14 |

|      |            |         | Table 2.65 IrDA I/O Voltage                                |     |

|      |            |         | Table 2.66 I2C I/O Voltage                                 |     |

|      |            |         | Table 2.67 SMBus I/O Voltage                               |     |

|      | 2.2        | AC S    | Specification                                              |     |

|      |            |         | PCI-Bus AC Spec.                                           |     |

|      |            |         | Universal Serial Bus (USB) AC Spec.                        |     |

|      |            | 2.2.3   | Audio AC Spec.                                             |     |

|      |            | 2.2.4   | VGA AC Spec.                                               |     |

|      |            | 2.2.5   | LCD AC Spec.                                               |     |

|      |            | 2.2.6   | IDE AC Spec                                                |     |

|      |            | 2.2.7   | Ethernet AC Spec.                                          |     |

|      |            | 2.2.8   | TV-Out Bus AC Spec                                         |     |

|      |            | 2.2.9   | I2C AC Spec.                                               |     |

|      |            | -       | SMBus AC Spec                                              |     |

|      |            | 2.0.10  | Table 3.1 Convention and Terminology                       |     |

|      | 3.1        | Conr    | nector X1 (PCI-Bus, USB, Audio)                            |     |

|      | 0.1        | Com     | Table 3.2 Connector X1 Pin Assignments                     |     |

|      | າງ         | Conr    | nector X2 (ISA-Bus)                                        |     |

|      | J.Z        | Com     | Table 3.3 Connector X2 Pin Assignments                     |     |

|      | 3.3        | Conr    | nector X3 (VGA, LCD/LVDS, COM1/2, LPT/Floppy, IrDA, KB/MS, |     |

|      |            |         | $\frac{1}{1000}$                                           |     |

| TV-O | ut)        | 23      | Table 2.4. Connector V2 Din Accimmente                     | 22  |

|      | <b>~</b> 4 | 0       | Table 3.4 Connector X3 Pin Assignments                     |     |

|      | 3.4        | Conr    | nector X4 (IDE1, IDE2, Ethernet, Miscellaneous)            |     |

|      |            | D :     | Table 3.5 Connector X4 Pin Assignments                     |     |

| 2    | 4.1        |         | gn Guidelines                                              |     |

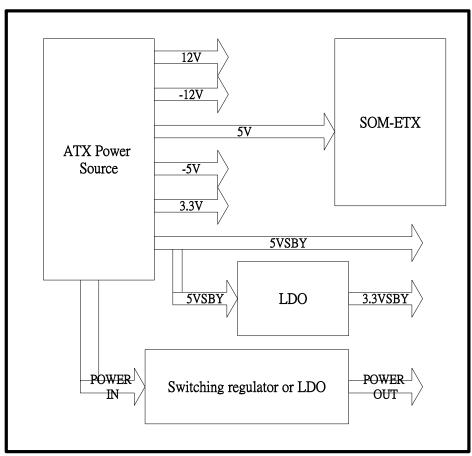

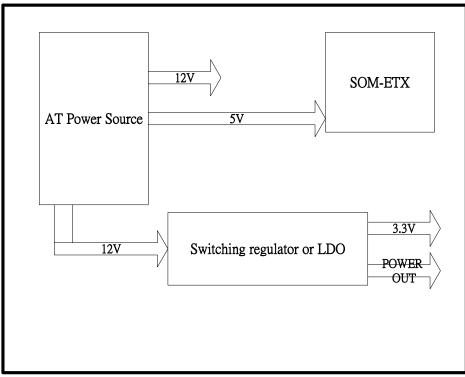

|      |            | 4.1.1   | ATX Power Delivery Block Diagram                           |     |

|      |            | 4.1.2   | AT Power Delivery Block Diagram                            |     |

| -    |            | 4.1.3   | Non-used 3.3V Pins on SOM Connector                        |     |

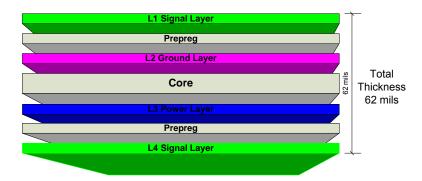

| Ę    | 5.1        |         | inal Board Stack-Up                                        |     |

|      |            | 5.1.1   | <b>y</b> 1                                                 |     |

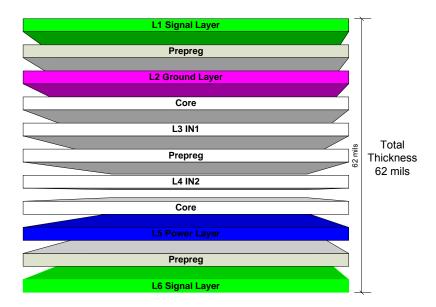

|      |            | 5.1.2   | Six layer board stack-up                                   |     |

|      |            |         | Table 5.2 Recommended 6-layer Board Stack-Up Dimensions    |     |

| Ę    | 5.2        | Alter   | native Stack-Ups                                           | .33 |

# AD\ANTECH EmbCore Advantech SOM-ETX Design Guide

| 6.1 PCI- | Bus                                                         | .34 |

|----------|-------------------------------------------------------------|-----|

| 6.1.1    | Signal Description                                          | .34 |

|          | Table 6.1 PCI Signal Description                            | .34 |

| 6.1.2    | Design Guidelines                                           |     |

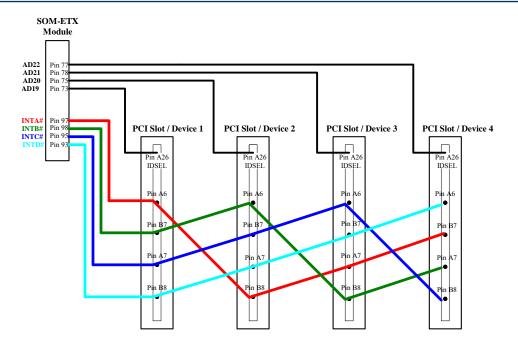

|          | Table 6.2 Carrier PCI Slots/Devices Interrupt Routing Table |     |

|          | Table 6.3 Clock Skew Parameters                             |     |

|          | Table 6.4 Maximum Add-in Card Loading via Each Power Rail . |     |

|          | Table 6.5 Add-in Card Supplied Power Selection              |     |

| 6.1.3    | Layout Guidelines                                           |     |

| 0.1.0    | Table 6.6 PCI Data Signals Routing Summary                  |     |

|          | Table 6.7 PCI Clock Signals Routing Summary                 |     |

| 6.1.4    | Application Notes                                           |     |

|          | /ersal Serial Bus (USB)                                     |     |

| 6.2.1    |                                                             |     |

| 0.2.1    | Signal Description                                          |     |

| 0.0.0    | Table 6.8 USB Signals Description                           |     |

| 6.2.2    | Design Guideline                                            |     |

| 6.2.3    |                                                             |     |

|          | io Codec 97(AC'97)                                          |     |

| 6.3.1    | Signal Description                                          |     |

|          | Table 6.9 Audio Signals Description                         |     |

| 6.3.2    | Design Note                                                 |     |

| 6.3.3    | Layout Guideline                                            |     |

| 6.4 ISA- | Bus                                                         |     |

| 6.4.1    | Signal Description                                          |     |

|          | Table 6.11 ISA Bus Signals Description                      |     |

| 6.4.2    | Design Guideline                                            | .50 |

| 6.4.3    | Layout Guideline                                            | .51 |

| 6.5 VGA  | ۱                                                           | .52 |

| 6.5.1    | Signal Description                                          | .52 |

|          | Table 6.12 VGA Signals Description                          |     |

| 6.5.2    | Design Guideline                                            |     |

| 6.5.3    | Layout Guideline                                            |     |

| 6.6 LVD  | S/TTL LCD                                                   |     |

| 6.6.1    | Signal Description                                          |     |

|          | Table 6.13 LVDS and TTL Signals Description                 |     |

| 6.6.2    |                                                             |     |

| 0.0.2    | Table 6.14 LVDS, TTL LCD Pin-out                            |     |

| 6.6.3    | Layout Guideline                                            |     |

|          | D/IDE1                                                      |     |

| 6.7.1    | Signal Description                                          |     |

| 0.7.1    | Table 6.15 IDE Signals Description                          |     |

| 6.7.2    | •                                                           |     |

| 6.7.3    | Layout Guideline                                            |     |

| 0.7.5    | Table 6.16 IDE Signal Groups                                |     |

|          |                                                             |     |

|          | Table 6.17 IDE Routing Summary                              |     |

|          | ernet                                                       |     |

| 6.8.1    | Signal Description                                          |     |

|          | Table 6.18 Ethernet Signals Description                     |     |

| 6.8.2    | Design Guideline                                            |     |

| 6.8.3    | Layout Guideline                                            |     |

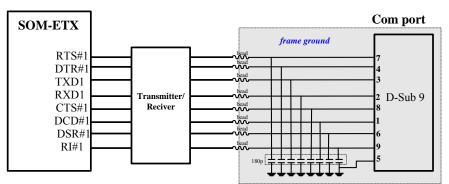

|          | al Port(Com1/Com2)                                          |     |

| 6.9.1    | Signal Description                                          |     |

|          | Table 6.19 Serial Bus Signals Description                   |     |

| 6.9.2    | Design Note                                                 |     |

| 6.9.3    | Layout Guideline                                            | .66 |

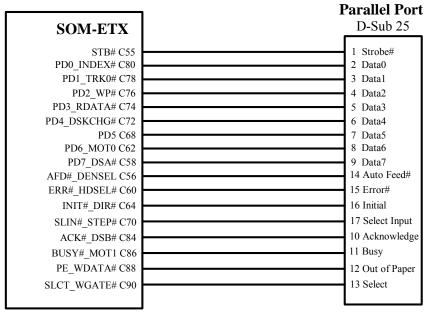

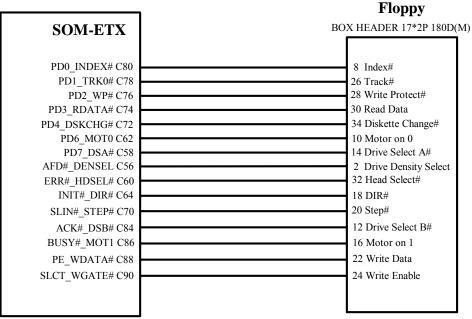

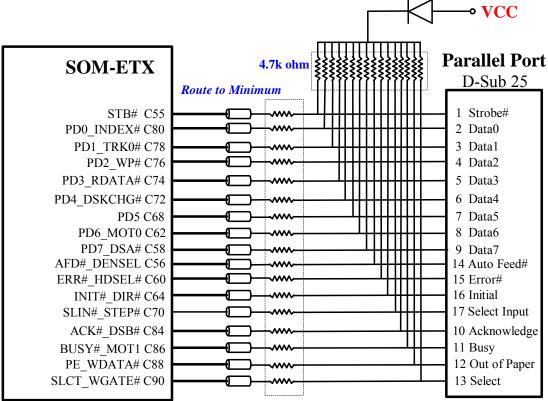

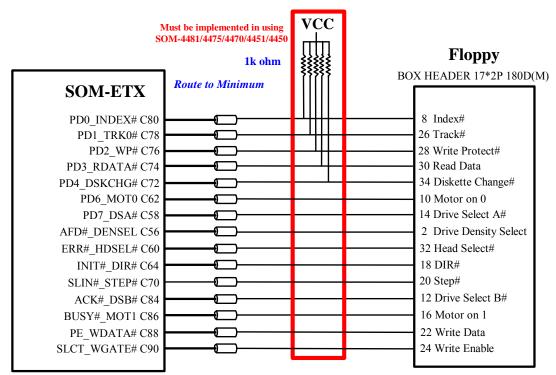

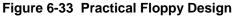

| 6.10 LPT/Floppy                                                              | 66  |

|------------------------------------------------------------------------------|-----|

| 6.10.1 Signal Description                                                    |     |

| Table 6.20 LTP/Floppy Signals Description                                    |     |

| 6.10.2 Design Note                                                           |     |

| 6.10.3 Layout Guideline                                                      |     |

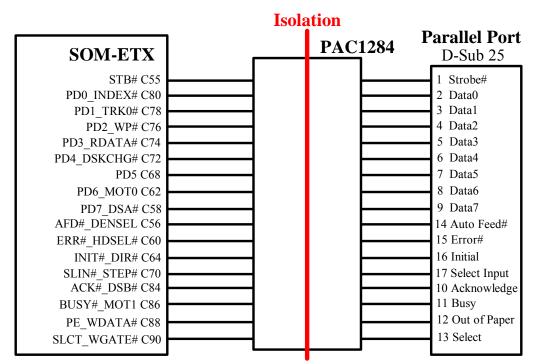

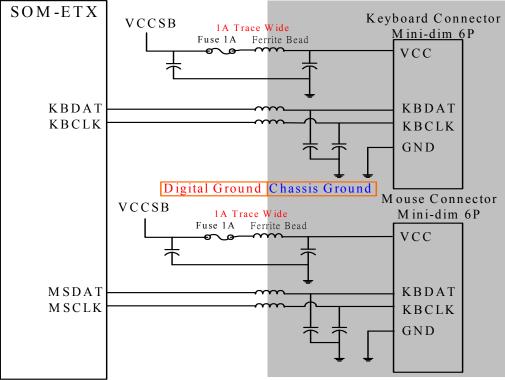

| 6.11 PS/2 Keyboard and Mouse                                                 |     |

| 6.11.1 Signal Description                                                    |     |

| Table 6.22 KB/MS Signals Description                                         |     |

| 6.11.2 Design Recommendation                                                 |     |

| 6.11.3 Layout Guideline                                                      |     |

| 6.11.4 EMI Consideration                                                     |     |

| 6.11.5 ESD Protection                                                        |     |

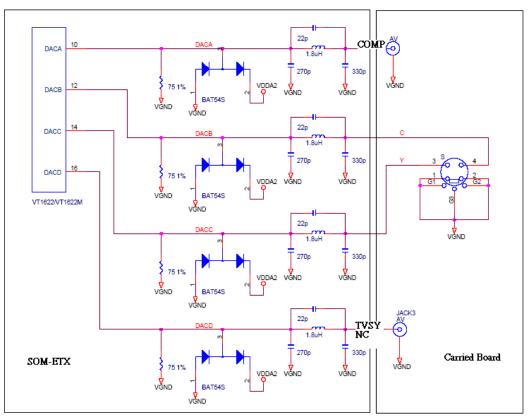

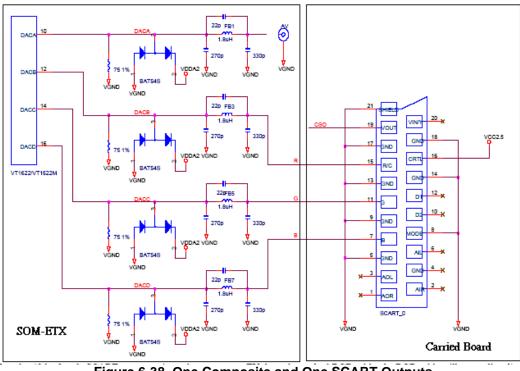

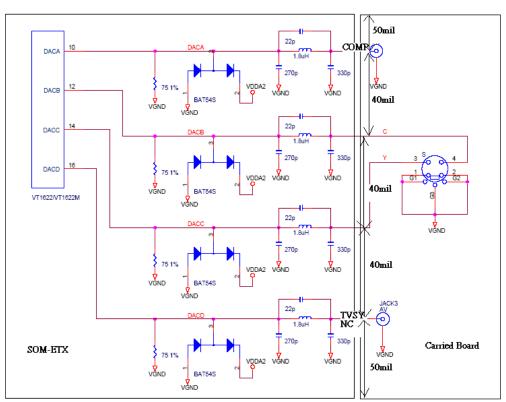

| 6.12 TV-Out                                                                  |     |

| 6.12.1 Signal Description                                                    |     |

| Table 6.23 TV Signals Description                                            |     |

| 6.12.2 Design Guideline                                                      |     |

| 6.12.3 Layout Guideline                                                      |     |

| 6.13 IrDA                                                                    |     |

| 6.13.1 Signal Description                                                    |     |

|                                                                              |     |

| Table 6.24 IrDA Signals Description                                          |     |

| 6.13.2 Design Guideline                                                      |     |

| 6.13.3 Layout Guideline                                                      |     |

| 6.14 Miscellaneous                                                           |     |

| 6.14.1 Miscellaneous Signal Description                                      |     |

| Table 6.25 Misc Signal Descriptions                                          |     |

| 6.14.2 Speaker                                                               | 81  |

| 6.14.3 Battery 82                                                            |     |

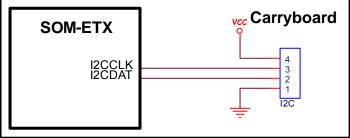

| 6.14.4 I2C Bus                                                               | 82  |

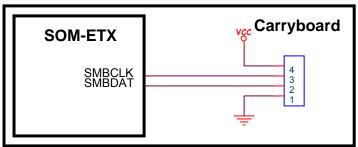

| 6.14.5 SMBus83                                                               |     |

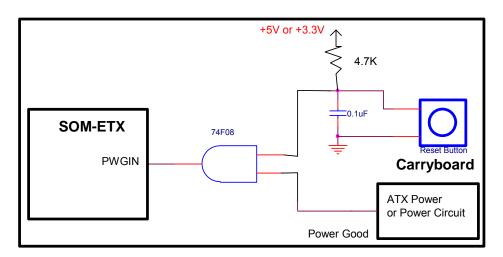

| 6.14.6 Power Good / Reset Input                                              |     |

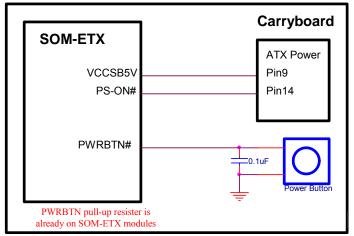

| 6.14.7 ATX Power Supply Control                                              |     |

| 6.14.8 External SMI Interrupt                                                |     |

| 6.14.9 Wake on Ring                                                          |     |

| 7.1 SOM-ETX Mechanical Dimensions                                            | 87  |

| Table 7.1 Connector Types                                                    | 87  |

| 7.1.1 Hirose FX8 and FX8C Series Information (reference to Hiro              | se  |

| Spec) 89                                                                     |     |

| Table 7.2 Hirose FX8 and FX8C Series info                                    | 89  |

| Table 7.3 Hirose FX8 and FX8C Series info                                    | 89  |

| 8.1 Material of Heatsink                                                     | 91  |

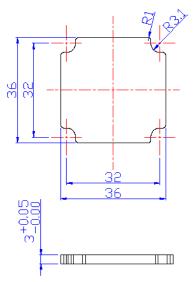

| 8.2 Thermal Interface Material                                               | 92  |

| 8.3 Attachment Method of Thermal Solution                                    | 92  |

| 8.4 Grounding Issues                                                         |     |

| 8.5 Air intake clearance and Airflow of Heatsink                             |     |

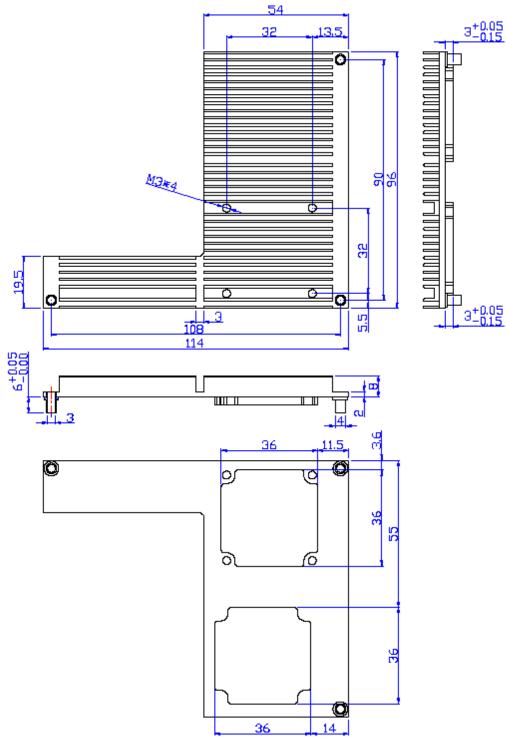

| 8.6 EXT-SOM Heatsink Specification                                           |     |

| 8.7 Advantech Heatsink Information                                           |     |

| 8.7.1 Heatsink                                                               |     |

| Table 8.1 Chemical Makeup & Temper Designation                               |     |

| Table 8.2 Chemical Makeup & Temper Designation                               |     |

| Table 8.3 Mechanical Characteristics                                         |     |

| Table 8.4 Chemical Makeup & Temper Designation                               |     |

| Table 8.5 Thermal pad                                                        |     |

| 8.7.2 Vendor List                                                            |     |

|                                                                              |     |

| Table 8.6 Vandar list Aluminum Extruded Last Sink                            |     |

| Table 8.6 Vendor list Aluminum Extruded Heat Sink,         8.7.3 Thermal Pad | 100 |

|       | Table 8.7 Thermal pad                  | 100 |

|-------|----------------------------------------|-----|

| 8.7.4 | Screw 100                              |     |

|       | Table 8.8 Screw                        | 100 |

| 8.7.5 | Fan 101                                |     |

|       | Table 8.9 Fan Physical Characteristics | 101 |

## Figure Summary

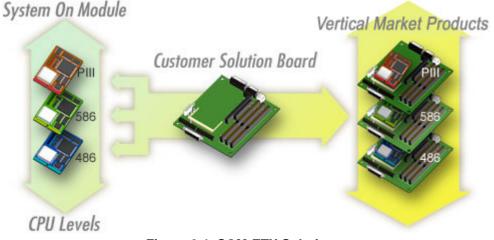

| Figure 2-1  | SOM-ETX Solutions                                                       | 10  |

|-------------|-------------------------------------------------------------------------|-----|

| Figure 2-2  | SOM-ETX Module and Carrier Board                                        |     |

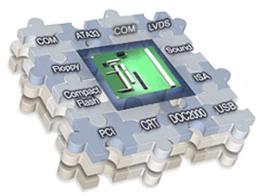

| Figure 2-3  | SOM-ETX Functions                                                       | .11 |

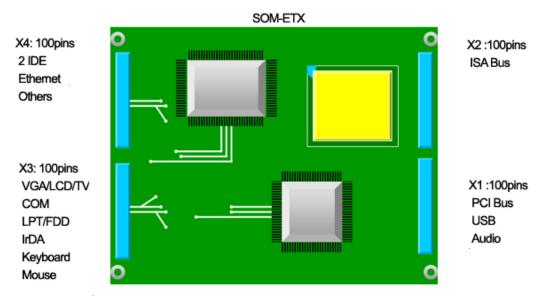

| Figure 3-1  | SOM-ETX, X1- X4 Diagram (Button View)                                   | 17  |

| Figure 4-1  | ATX Power Delivery Block Diagram                                        | 28  |

| Figure 4-2  | AT Power Delivery Block Diagram                                         | 29  |

| Figure 5-1  | Four-Layer Stack-up with 2 Signal Layers and 2                          |     |

|             | Power Planes                                                            | 31  |

| Figure 5-2  | Six-Layer Stack-up with 4 Signal Layers and 2                           |     |

|             | Power Planes                                                            | 69  |

| Figure 6-1  | Routing PCI Slot/Device CSB Interrupt                                   |     |

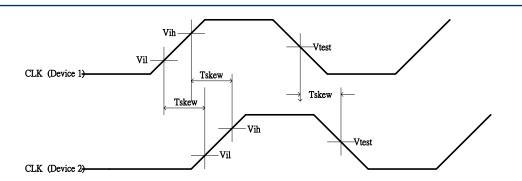

| Figure 6-2  | Clock Skew Diagram                                                      | 37  |

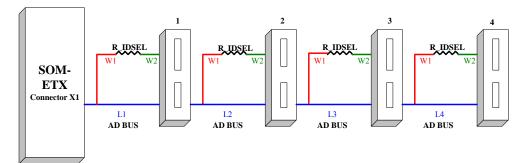

| Figure 6-3  | PCI Bus Layout Example with IDSEL                                       |     |

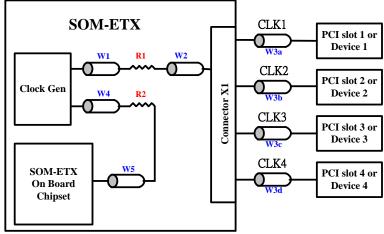

| Figure 6-4  | PCI Clock Layout Example                                                |     |

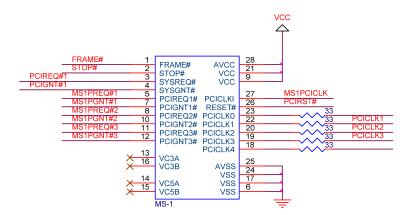

| Figure 6-5  | Design Example PCI Arbiter                                              |     |

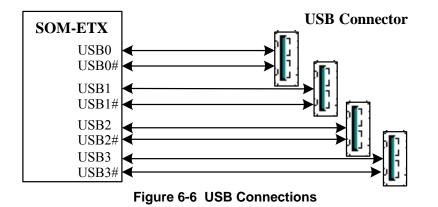

| Figure 6-6  | USB Connections                                                         |     |

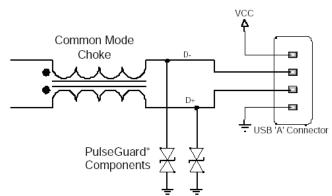

| Figure 6-7  | Common Mode Choke                                                       |     |

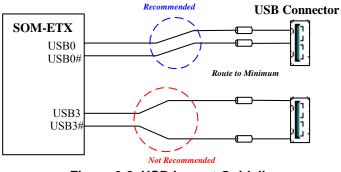

| Figure 6-8  | USB Layout Guidelines                                                   |     |

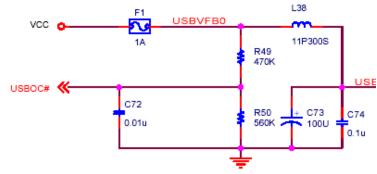

| Figure 6-9  | Over-Current Circuit.                                                   |     |

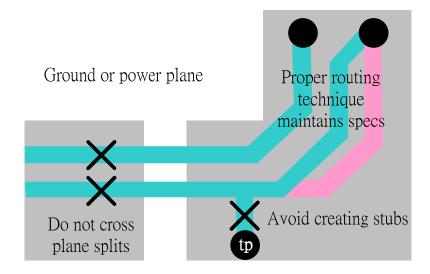

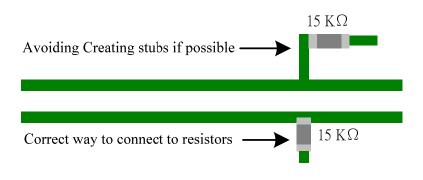

|             | Violation of Proper Routing Techniques                                  |     |

|             | Creating Unnecessary Stubs                                              |     |

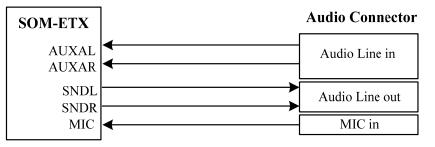

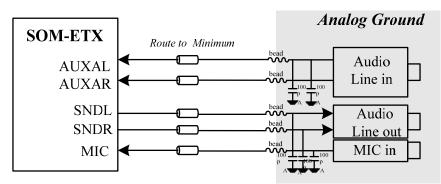

|             | Audio Connetions                                                        |     |

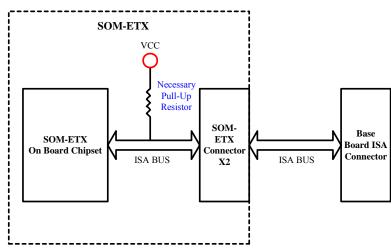

|             | Audio Layout Guidelines<br>ISA BUS Necessary Pull-up Resistors Location |     |

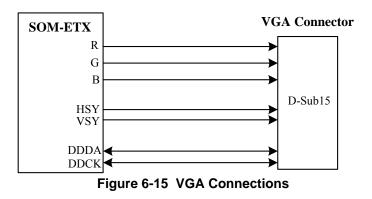

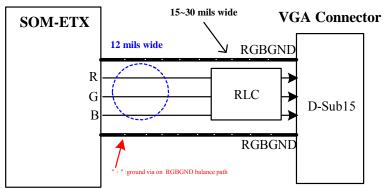

|             | VGA Connections                                                         |     |

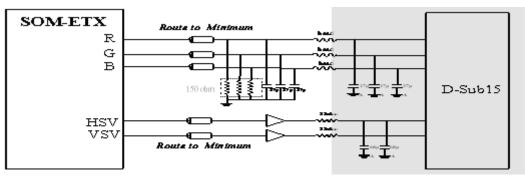

|             | VGA Connections                                                         |     |

|             | RGB Output Layout Guidelines                                            |     |

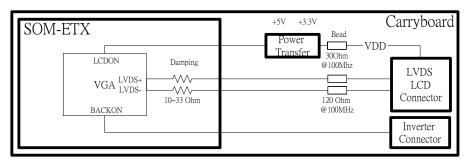

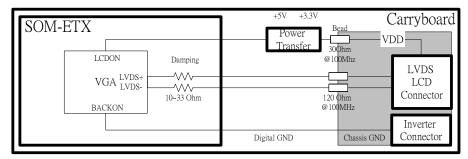

|             | LVDS LCD Connections                                                    |     |

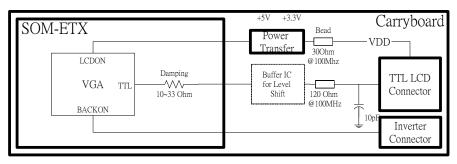

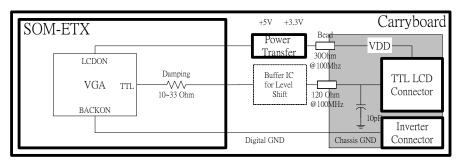

|             | TTL LCD Connections                                                     |     |

|             | LVDS LCD Layout Guidelines                                              |     |

| •           | TTL LCD Layout Guidelines                                               |     |

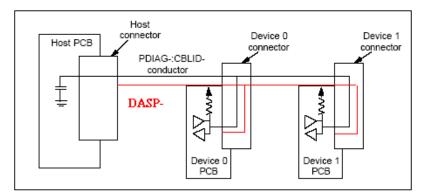

|             | IDE Master/Slave Handshake Signals Connection.                          |     |

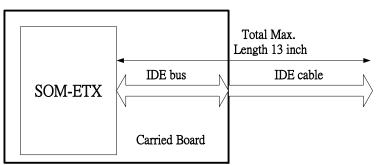

|             | IDE Bus Trace on Carrier Board and Cable Length                         |     |

|             | Limitation                                                              | 60  |

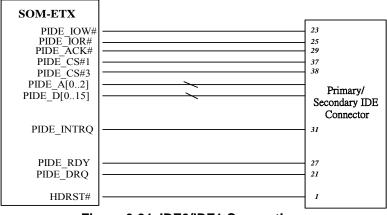

| Figure 6-24 | IDE0/IDE1 Connections                                                   | .63 |

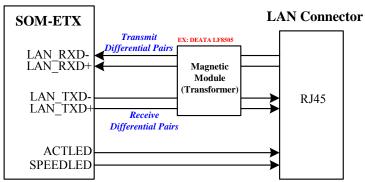

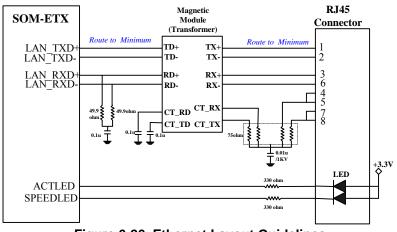

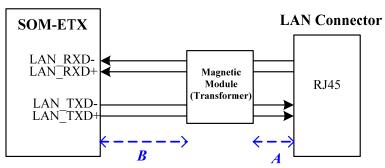

|             | 10/100M Ethernet Connections                                            |     |

|             | Ethernet Layput Guidelines                                              |     |

|             | Critical Dimensions                                                     |     |

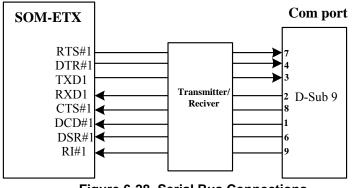

|             | Serial Bus Connections                                                  |     |

|             | Serial Bus Layout Guidelines                                            |     |

| Figure 6-30 | LPT Connections                                                         | 72  |

| Figure 6-31 | Floppy Connections                                                      | 72  |

|             | Practical LPT Port Design                                               |     |

|             | Practical Floppy Design                                                 |     |

| Figure 6-34 | Practical LPT Port Design Using PAC1284                                 | .73 |

| Figure 6-36<br>Figure 6-37<br>Figure 6-38 | Keyboard and Mouse Connections74Practical KB/MS Circuit74Two Composite and One S-Video Outputs76One Composite and One SCART Outputs76TV DAC Signal Routing Spacing77 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

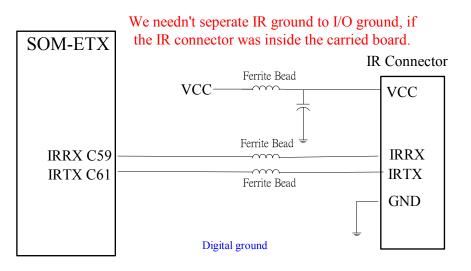

|                                           | IrDA Connections(IR connector on digital ground)78                                                                                                                   |

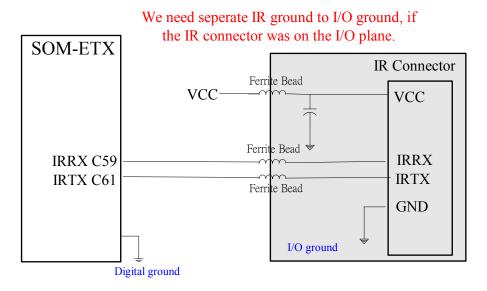

|                                           | IrDA Connections(IR connector on I/O ground)79                                                                                                                       |

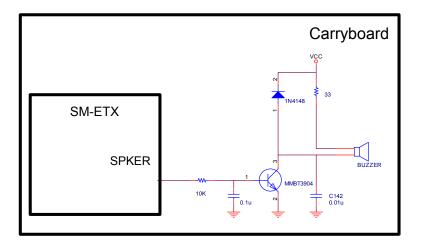

|                                           | Speaker Connections81                                                                                                                                                |

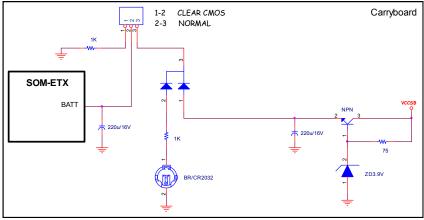

|                                           | Battery Connections82                                                                                                                                                |

|                                           | I2C Bus Connections82                                                                                                                                                |

|                                           | SMBus Connections83                                                                                                                                                  |

| •                                         | Power Good / Reset Input Connections                                                                                                                                 |

|                                           | ATX Power Supply Connections                                                                                                                                         |

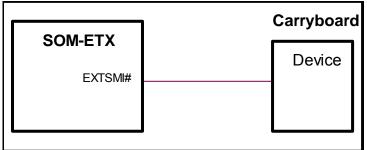

| •                                         | External SMI Interrupt Connections                                                                                                                                   |

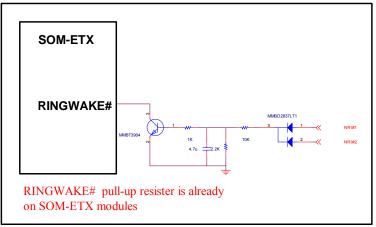

|                                           | Wake on Ring Connections(two Comport)                                                                                                                                |

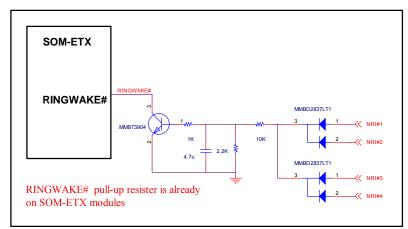

|                                           | Wake on Ring Connections(multiple Comport)86                                                                                                                         |

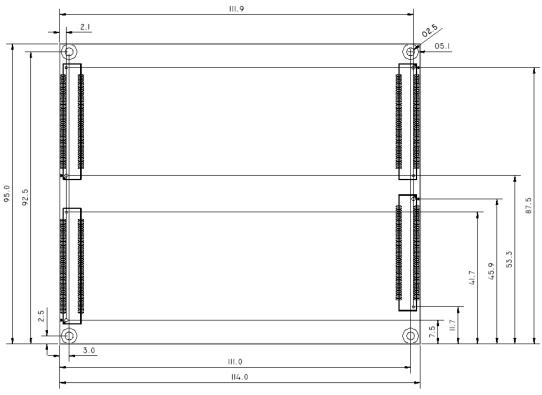

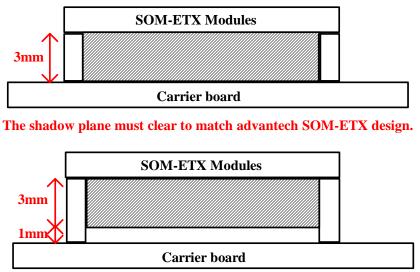

| 0                                         | SOM-ETX Carrier Board Mechanical Dimensions87                                                                                                                        |

| Figure 7-2                                |                                                                                                                                                                      |

| Figure 7.2                                | Dimensions                                                                                                                                                           |

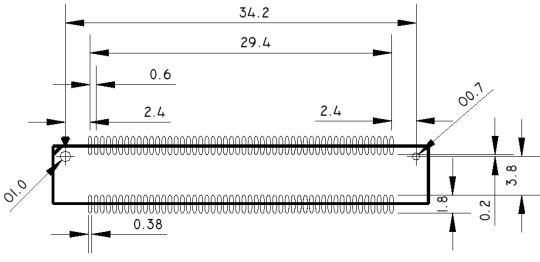

| Figure 7-3                                | Connector Hirose FX8-100 Footprint                                                                                                                                   |

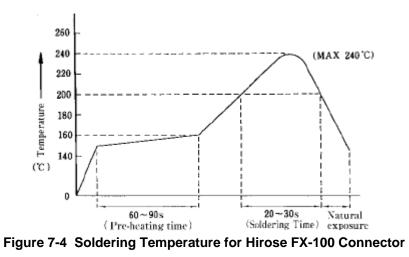

| Figure 7-4                                | Soldering Temperature for Hirose FX-100<br>Connector                                                                                                                 |

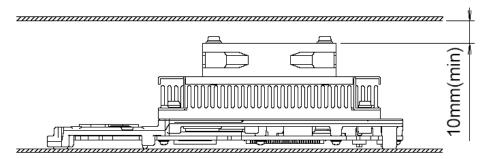

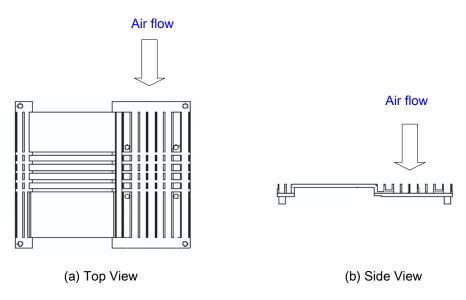

| Figure 8-1                                | Air Intake Clearance                                                                                                                                                 |

| Figure 8-2                                | Air Flow Direction                                                                                                                                                   |

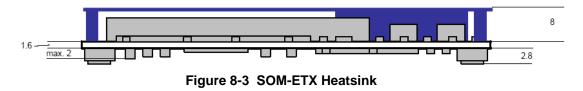

| Figure 8-3                                | SOM-ETX Heatsink                                                                                                                                                     |

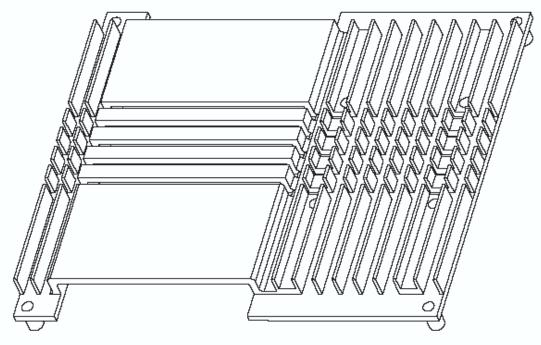

| Figure 8-4                                | Heatsink Appearance                                                                                                                                                  |

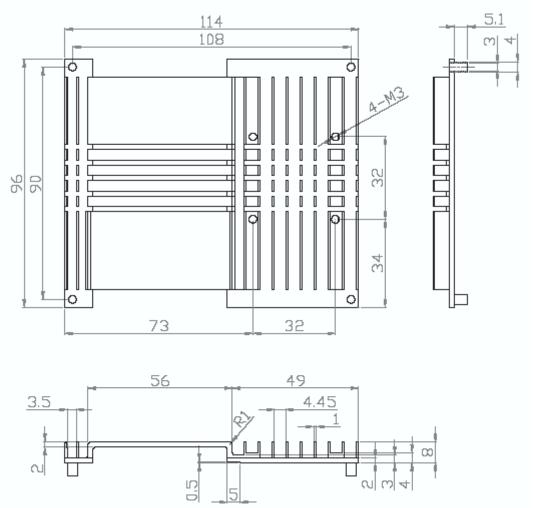

| Figure 8-5                                | Heatsink Dimensions                                                                                                                                                  |

| Figure 8-6                                | Heatsink Dimensions                                                                                                                                                  |

| Figure 8-7                                | Heatsink Dimensions                                                                                                                                                  |

| Figure 8-8                                | Heatsink Dimensions                                                                                                                                                  |

| Figure 8-9                                | Thermal Pad100                                                                                                                                                       |

| •                                         | Fan Appearance101                                                                                                                                                    |

| -                                         |                                                                                                                                                                      |

## Chapter 1 Introduction

The design guide organizes and provides Advantech SOM baseboard design recommendations for Advantech SOM-ETX modules. It specifies common mechanical and electrical characteristics in order to ensure the baseboard design meets these requirements and works properly.

## 1.1 Terminology

| Table 1.1 Conventions a | nd Terminology                                                                                                                        |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AC97                    | Audio Codec 97'                                                                                                                       |  |  |

| AGP                     | Accelerated Graphics port refers to the AGP/PCI interface                                                                             |  |  |

| CPU                     | Central processing Unit                                                                                                               |  |  |

| CRT                     | Cathode Ray Tube                                                                                                                      |  |  |

| DDR                     | Double Data Rate SDRAM memory technology                                                                                              |  |  |

| DTOS                    | Advantech's Design To Order Service                                                                                                   |  |  |

| EMI                     | Electromagnetic Interference                                                                                                          |  |  |

| ESD                     | Electrostatic Discharge                                                                                                               |  |  |

| ETX                     | Embedded Technology Extended                                                                                                          |  |  |

| FSB                     | Front Side Bus, synonymous with Host or CPU bus                                                                                       |  |  |

| GMCH                    | Refers to the Graphics Memory Controller Hub chipset component                                                                        |  |  |

| 12C                     | Inter-IC (a two wire serial bus created by Philips)                                                                                   |  |  |

| ISA                     | International Standards Association                                                                                                   |  |  |

| IDE (ATA)               | Integrated Drive Electronics (Advanced Technology Attachment)                                                                         |  |  |

| INTx                    | An interrupt request signal where x stands for interrupts A, B, C, and D.                                                             |  |  |

| LCD                     | Liquid Crystal Display                                                                                                                |  |  |

| LVDS                    | Low Voltage Differential Signaling: A high speed, low power data<br>transmission standard used for display connections to LCD panels. |  |  |

| MCH                     | Refers to the Memory Controller Hub chipset component                                                                                 |  |  |

| NTSC                    | National Television Standards Committee                                                                                               |  |  |

| PAL                     | Phase Alternate Line                                                                                                                  |  |  |

| PCI                     | Peripheral Component Interface                                                                                                        |  |  |

| RTC                     | Real Time Clock                                                                                                                       |  |  |

| SMBus                   | System Management Bus                                                                                                                 |  |  |

| SMI                     | System Management Interrupt                                                                                                           |  |  |

| SOM                     | System On Module                                                                                                                      |  |  |

| ULV                     | Ultra-Low Voltage                                                                                                                     |  |  |

| USB                     | Universal Serial Bus                                                                                                                  |  |  |

## **1.2 Referenced Documents**

| Table 1.2 Referenced Documents                                                       |                                                   |  |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| Document                                                                             | Location                                          |  |  |  |

| Advanced Configuration<br>and Power Management<br>(ACPI) Specification 1.0b &<br>2.0 | http://www.teleport.com/~acpi/                    |  |  |  |

| Advanced Power<br>Management (APM)<br>Specification 1.2                              | http://www.microsoft.com/hwdev/busbios/amp_12.htm |  |  |  |

| Ethernet(IEEE 802.3)                                                                 | http://www.ieee.org/portal/site                   |  |  |  |

| I2C Bus Interface                                                                    | http://www.semiconductors.philips.com/            |  |  |  |

| IrDA                                                                                 | http://www.irda.org/                              |  |  |  |

| PCI                                                                                  | http://www.pcisig.com/                            |  |  |  |

| PC104                                                                                | http://www.pc104.org/technology/pc104_tech.html   |  |  |  |

| RS232                                                                                | http://www.eia.org/                               |  |  |  |

| SMBus                                                                                | http://www.smbus.org/specs/                       |  |  |  |

| USB                                                                                  | http://www.usb.org/home                           |  |  |  |

## Chapter 2 SOM-ETX Specification

SOM-ETX provides a scalable solution that meets customer's advanced CPU application development needs and reduces time-to-market. Using SOM-DTOS, customers can reduce traditional customized CPU board development time and costs by as much as 80%.

## 2.1 Overview

Advantech offers a wide range of SOM products to cater to each customer's demands. The modular designs allow upgrade ability and add more flexibility to the system. The SOM-ETX form factor allows the CPU modules to be easily and securely mounted on a customized solution board. The design and multiple processor choices eliminate CPU integration worries and allow fast application support for the most dynamic embedded needs.

Figure 2-1 SOM-ETX Solutions

SOM-ETX is a series of reliable and widely used CPU cores with high integration features. It can support fanless operation in small form factors while supporting CPUs ranging from GX1 to Pentium M. Not only does SOM-ETX allow quick design, it also provides the benefits of easy installation, maintenance and upgrade ease.

Figure 2-2 SOM-ETX Module and Carrier Board

Though small in size, SOM-ETX takes care of most complicated CPU architectures and basic common circuits. Many system integrators are finding an Advantech SOM-ETX solution already covers 80% of their feature requirements. This makes SOM-ETX a powerful time and money saver.

Figure 2-3 SOM-ETX Functions

SOM-ETX + Customer Solution Board = Your Customized Platform which perfectly fits system-level requirements and saves time and reduces total project management cost.

## Interface I/O Voltage

#### 2.1.1.1 PCI Bus

| Table 2.53 DC Specifications for 5V Signaling of PCI Bus |                     |      |         |       |      |  |

|----------------------------------------------------------|---------------------|------|---------|-------|------|--|

| Symbol                                                   | Parameter           | Min  | Max     | Units | Note |  |

| Vcc                                                      | Supply Voltage      | 4.75 | 5.25    | V     |      |  |

| Vih                                                      | Input High Voltage  | 2.0  | Vcc+0.5 | V     |      |  |

| Vil                                                      | Input Low Voltage   | -0.5 | 0.8     | V     |      |  |

| Voh                                                      | Output High Voltage | 2.4  | -       | V     |      |  |

| Vol                                                      | Output Low Voltage  | -    | 0.55    | V     | *1   |  |

\*1. Signals without pull-up resistors must have 3 mA low output current. Signals requiring pull up must have 6 mA; the latter include, FRAME#, TRDY#, IRDY#, DEVSEL#, STOP#, SERR#, PERR#, LOCK#, INTA#, INTB#, INTC#, INTD#.

| Table 2.54 DC Specifications for 3.3V Signaling of PCI Bus |                       |        |         |       |      |

|------------------------------------------------------------|-----------------------|--------|---------|-------|------|

| Symbol                                                     | Parameter             | Min    | Max     | Units | Note |

| Vcc                                                        | Supply Voltage        | 3.0    | 3.6     | V     |      |

| Vih                                                        | Input High Voltage    | 0.5Vcc | Vcc+0.5 | V     |      |

| Vil                                                        | Input Low Voltage     | -0.5   | 0.3Vcc  | V     |      |

| Vipu                                                       | Input Pull-up Voltage | 0.7Vcc | -       | V     | *1   |

| Voh                                                        | Output High Voltage   | 0.9Vcc | -       | V     |      |

| Vol                                                        | Output Low Voltage    | -      | 0.1Vcc  | V     |      |

\*1. This specification should be guaranteed by design. It is the minimum voltage to which pullup resistors are calculated to pull a floated network. Applications sensitive to static power utilization must assure that the input buffer is conducting minimum current at this input voltage.

## 2.1.1.2 Universal Serial Bus (USB)

| Table 2.55 DC Specification of USB Signals |                                |      |      |      |      |

|--------------------------------------------|--------------------------------|------|------|------|------|

| Symbol                                     | Parameter                      | Min  | Max  | Unit | Note |

| V <sub>bus</sub>                           | High-power port supply voltage | 4.75 | 5.25 | V    |      |

| V <sub>bus</sub>                           | Low-power port supply voltage  | 4.75 | 5.25 | V    |      |

| VIL                                        | Input Low Voltage              | -    | 0.8  | V    |      |

| VIH                                        | Input High Voltage(driven)     | 2.0  | -    | V    |      |

| V <sub>IHZ</sub>                           | Input High Voltage(floating)   | 2.7  | 3.6  | V    |      |

| Vol                                        | Output Low Voltage             | 0    | 0.3  | V    |      |

| V <sub>OH</sub>                            | Output High Voltage            | 2.8  | 3.6  | V    |      |

## 2.1.1.3 Audio

| Table 2.56 AC'97 CODEC DC Specifications |                        |         |         |      |      |  |  |  |  |

|------------------------------------------|------------------------|---------|---------|------|------|--|--|--|--|

| Symbol                                   | Parameter              | Min     | Max     | Unit | Note |  |  |  |  |

| Dvdd                                     | Digital supply voltage | Dvdd+5% | Dvdd+5% | V    |      |  |  |  |  |

| Avdd                                     | Analog supply voltage  | 4.75    | 5.25    | V    |      |  |  |  |  |

| Vil                                      | Input Low Voltage      | -       | 0.35Vdd | V    |      |  |  |  |  |

| Vih                                      | Input High Voltage     | 0.65Vdd | -       | V    |      |  |  |  |  |

\*1. Dvdd=5V or 3.3V

| Table 2.57 AC'97 CODEC Analog I/O DC Specifications |                           |     |     |     |      |      |  |  |  |

|-----------------------------------------------------|---------------------------|-----|-----|-----|------|------|--|--|--|

| Symbol                                              | Parameter                 | Min | Тур | Max | Unit | Note |  |  |  |

| AUXAL/R                                             | Full scale input voltage  | -   | 1.0 | -   | Vrms |      |  |  |  |

| MIC                                                 | Full scale input voltage  | -   | 0.1 | -   | Vrms |      |  |  |  |

| SNDL/R                                              | Full scale output voltage | -   | 1.0 | -   | Vrms |      |  |  |  |

#### 2.1.1.4 VGA

| Table 2.58 Hsync and Vsync Signals Specifications |                     |     |     |      |      |  |  |  |  |

|---------------------------------------------------|---------------------|-----|-----|------|------|--|--|--|--|

| Symbol                                            | Parameter           | Min | Max | Unit | Note |  |  |  |  |

| VIL                                               | Input Low Voltage   | 0   | 0.5 | V    |      |  |  |  |  |

| VIH                                               | Input High Voltage  | 2.4 | 5.5 | V    |      |  |  |  |  |

| V <sub>OL</sub>                                   | Output Low Voltage  | -   | 0.8 | V    |      |  |  |  |  |

| V <sub>OH</sub>                                   | Output High Voltage | 2.0 | -   | V    |      |  |  |  |  |

| Table 2.59 | Table 2.59 RGB Voltage                                     |             |            |      |      |  |  |  |  |

|------------|------------------------------------------------------------|-------------|------------|------|------|--|--|--|--|

| Symbol     | Parameter                                                  | Min         | Max        | Unit | Note |  |  |  |  |

| R          | Red analog video output signal<br>Max. luminance voltage   | 0.665       | 0.77       | V    |      |  |  |  |  |

| G          | Green analog video output signal<br>Max. luminance voltage | 0.665       | 0.665 0.77 |      |      |  |  |  |  |

| В          | Blue analog video output signal<br>Max. luminance voltage  | 0.665       | 0.665 0.77 |      |      |  |  |  |  |

| R          | Red analog video output signal<br>min. luminance voltage   | 0 (Typical) |            | V    |      |  |  |  |  |

| G          | Green analog video output signal min. luminance voltage    | 0 (Typical) |            | V    |      |  |  |  |  |

| В          | Blue analog video output signal<br>min. luminance voltage  | 0 (Typical) |            | V    |      |  |  |  |  |

## 2.1.1.5 LCD

| Table 2.60 LCD I/O Voltage |                     |      |         |      |            |  |  |  |  |

|----------------------------|---------------------|------|---------|------|------------|--|--|--|--|

| Symbol                     | Parameter           | Min  | Max     | Unit | Note       |  |  |  |  |

| VIL                        | Input Low Voltage   | -0.5 | 0.8     | V    |            |  |  |  |  |

| VIH                        | Input High Voltage  | 2.0  | Vcc+0.5 | V    |            |  |  |  |  |

| Vol                        | Output Low Voltage  | -    | 0.55    | V    | Iol=4.0mA  |  |  |  |  |

| V <sub>OH</sub>            | Output High Voltage | 2.4  | -       | V    | loh=-1.0mA |  |  |  |  |

## 2.1.1.6 IDE

| Table 2.61 Ultra DMA modes 1-4 (5V) |                     |     |     |      |      |  |  |  |  |

|-------------------------------------|---------------------|-----|-----|------|------|--|--|--|--|

| Symbol                              | Parameter           | Min | Max | Unit | Note |  |  |  |  |

| V <sub>IH</sub>                     | Input High Voltage  | -   | 5.5 | V    |      |  |  |  |  |

| V <sub>OL</sub>                     | Output Low Voltage  | -   | 0   | V    |      |  |  |  |  |

| V <sub>OH</sub>                     | Output High Voltage | 2   | -   | V    |      |  |  |  |  |

| Table 2.62 Ultra DMA modes 5 (3.3V) |                                            |        |        |      |      |  |  |  |  |

|-------------------------------------|--------------------------------------------|--------|--------|------|------|--|--|--|--|

| Symbol                              | Parameter                                  | Min    | Max    | Unit | Note |  |  |  |  |

| V <sub>dd3</sub>                    | DC supply voltage to drivers and receivers | 3.3-8% | 3.3+8% | V    |      |  |  |  |  |

| V+                                  | Low to High input threshold                | 1.5    | 2.0    | V    |      |  |  |  |  |

| V.                                  | High to Low input threshold                | 1.0    | 1.5    | V    |      |  |  |  |  |

## 2.1.1.7 Ethernet

| Table 2.63 Ethernet I/O Voltage |                     |        |         |      |      |  |  |  |  |

|---------------------------------|---------------------|--------|---------|------|------|--|--|--|--|

| Symbol                          | Parameter           | Min    | Max     | Unit | Note |  |  |  |  |

| VIL                             | Input Low Voltage   | -0.5   | 0.3Vcc  | V    | *1   |  |  |  |  |

| VIH                             | Input High Voltage  | 0.5Vcc | Vcc+0.5 | V    |      |  |  |  |  |

| V <sub>OL</sub>                 | Ouput Low Voltage   | -      | 0.1Vcc  |      |      |  |  |  |  |

| V <sub>OH</sub>                 | Output High Voltage | 0.9Vcc | Vcc     |      |      |  |  |  |  |

\*1. Vcc=3.0V min. to 3.6V max.

#### 2.1.1.8 TV-Out Bus

| Table 2.64 TV-Out I/O Voltage |                    |      |      |      |             |  |  |  |  |

|-------------------------------|--------------------|------|------|------|-------------|--|--|--|--|

| Symbol                        | Parameter          | Min  | Max  | Unit | Note        |  |  |  |  |

| Vo                            | Output Voltage     | 1.28 | 1.28 | V    | Typical=1.8 |  |  |  |  |

| V <sub>IH</sub>               | Input High Voltage | 0    | 1.4  | V    |             |  |  |  |  |

#### 2.1.1.9 IrDA

| Table 2.65 IrDA I/O Voltage |                                                |      |         |      |               |  |  |  |  |

|-----------------------------|------------------------------------------------|------|---------|------|---------------|--|--|--|--|

| Symbol                      | Parameter                                      | Min  | Max     | Unit | Note          |  |  |  |  |

| V <sub>IL</sub>             | Input Low Voltage                              | -0.5 | 0.8     | V    |               |  |  |  |  |

| VIH                         | Input High Voltage                             | 2.0  | VCC+0.5 | V    |               |  |  |  |  |

| V <sub>OL</sub>             | Output Low Voltage                             | -    | 0.4     | V    |               |  |  |  |  |

| Voh                         | Output High Voltage                            | 2.4  | -       | V    |               |  |  |  |  |

| I <sub>Ldtx</sub>           | Input Load Current (IRTX Signal)               | -    | 6       | mA   | 0≦Vin<br>≦Vcc |  |  |  |  |

| ILd                         | Input Load Current (all signal<br>except IRTX) | -    | 1.5     | mA   | 0≦Vin<br>≦Vcc |  |  |  |  |

\*1. From "Infrared Data Association – Infrared Dongle Interface v1.1"

\*2. Vcc=5.0V±5%

## 2.1.1.10 I2C

| Table 2.66 I2C I/O Voltage |                       |        |         |      |      |  |  |  |  |

|----------------------------|-----------------------|--------|---------|------|------|--|--|--|--|

| Symbol                     | Parameter             | Min    | Max     | Unit | Note |  |  |  |  |

| V <sub>IL</sub>            | Input Low<br>Voltage  | -0.5   | 0.3Vdd  | V    |      |  |  |  |  |

| V <sub>IH</sub>            | Input High<br>Voltage | 0.7Vdd | Vdd+0.5 | V    |      |  |  |  |  |

| V <sub>OL</sub>            | Output Low<br>Voltage | 0      | 0.4     | V    |      |  |  |  |  |

\*1. The I2C Bus Specification V2.1.\*2. Vdd is the voltage which the pull-up resistor are connected.

### 2.1.1.11 SMBus

| Table 2.67 SMBus I/O Voltage |                       |     |     |      |      |  |  |  |

|------------------------------|-----------------------|-----|-----|------|------|--|--|--|

| Symbol                       | Parameter             | Min | Max | Unit | Note |  |  |  |

| V <sub>IL</sub>              | Input Low<br>Voltage  | -   | 0.8 | V    |      |  |  |  |

| V <sub>IH</sub>              | Input High<br>Voltage | 2.1 | Vdd | V    |      |  |  |  |

| V <sub>OL</sub>              | Output Low<br>Voltage | -   | 0.4 | V    |      |  |  |  |

\*1. System Management Bus (SMBus) Specification v2.0.\*2. Vdd is the voltage which the pull-up resistor are connected.

## 2.2 AC Specification

## 2.2.1 PCI-Bus AC Spec.

Refer to "PCI Local Bus Specification Revision 2.2 December 18, 1998" Chapter 4.2 for the details.

## 2.2.2 Universal Serial Bus (USB) AC Spec.

Refer to "Universal Serial Bus Specification Revision 1.1 September 23, 1998" Chapter 7 for the details.

## 2.2.3 Audio AC Spec.

Refer to "Audio Codec '97 Revision 2.1 May 22, 1998" Chapter 9 for digital signals AC spec. and Chapter 10 for analog performance spec.

## 2.2.4 VGA AC Spec.

Refer to "VESA and Industry Standards and Guidelines for Computer Display Monitor Timing Version 1.0, Revision 0.8" for the monitor timing specification.

## 2.2.5 LCD AC Spec.

Refer to "VT 8606 TwisterT Single-Chip SMA North Bridge with 133 / 100 / 66 MHz Front Side Bus for VIA<sup>™</sup> C3<sup>™</sup> and Intel<sup>™</sup> Celeron<sup>™</sup>, Pentium<sup>™</sup> III and III-M (Tualatin) CPUs with Integrated ProSavage4 AGP 4x Graphics plus Advanced Memory Controller supporting PC133 / PC100 SDRAM for Mobile PC Systems Revision 1.02 February 12, 2002" for the details.

## 2.2.6 IDE AC Spec.

Refer to "Information Technology - AT Attachment with Packet Interface – 7 Volume 2 (ATA/ATAPI-7 V2)" Annex B.5 for the details

## 2.2.7 Ethernet AC Spec.

Refer to "REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT RTL8139C(L)" datasheet chapter 11 for the details.

## 2.2.8 TV-Out Bus AC Spec.

Refer to "VT1622 and VT1622M Digital TV Encoders Revision 1.21 January 13, 2003"

## 2.2.9 I2C AC Spec.

Refer to "THE I 2C-BUS SPECIFICATION VERSION 2.1 JANUARY 2000" for the DAC AC Characteristics

## 2.6.10 SMBus AC Spec.

Refer to "System Management Bus (SMBus) Specification Version 2.0 August 3, 2000"

## Chapter 3 SOM-ETX Pin Assignment

This chapter describes pin assignments and I/O characteristics for 400 pins SOM-ETX (X1, X2, X3 and X4). X1 connector contains PCI-Bus, USB, Audio interfaces. X2 connector contains ISA-Bus. X3 connector contains VGA, LCD/LVDS, COM1/2, LPT/Floppy, IrDA, KB/MS and TV-Out interfaces. X4 connector contains IDE1, IDE2, Ethernet and miscellaneous.

Figure 3-1 SOM-ETX, X1- X4 Diagram (Button View)

| Table 3.1 Convention and Terminology |                          |                    |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------|--------------------|--|--|--|--|--|--|--|

| Convention                           | Description              | Example            |  |  |  |  |  |  |  |

| ·#'                                  | Active-Low Signals       | REQ0#              |  |  |  |  |  |  |  |

| '+' and '-'                          | Differential Pairs       | LAN_TXD+, LAN_TXD- |  |  |  |  |  |  |  |

|                                      |                          |                    |  |  |  |  |  |  |  |

| Terminology                          | Description              |                    |  |  |  |  |  |  |  |

| Pin Types:                           |                          |                    |  |  |  |  |  |  |  |

|                                      | Input                    |                    |  |  |  |  |  |  |  |

| 0                                    | Output                   |                    |  |  |  |  |  |  |  |

| 10                                   | Bi-Directional           |                    |  |  |  |  |  |  |  |

| OD                                   | Open Drain               |                    |  |  |  |  |  |  |  |

|                                      |                          |                    |  |  |  |  |  |  |  |

| Power Pin Types                      |                          |                    |  |  |  |  |  |  |  |

| VCC5                                 | +5V ±5% Volts            |                    |  |  |  |  |  |  |  |

| VSB5                                 | +5V ±5% Standby Power    |                    |  |  |  |  |  |  |  |

| VCC3                                 | +3.3V ±5% Volts          |                    |  |  |  |  |  |  |  |

| VSB3                                 | +3.3V ±5% Standby Power  |                    |  |  |  |  |  |  |  |

| VCC3/5                               | +3.3V and +5V tolerance  |                    |  |  |  |  |  |  |  |

| GND                                  | System Ground            |                    |  |  |  |  |  |  |  |

| PWR                                  | Power Supply             |                    |  |  |  |  |  |  |  |

|                                      |                          |                    |  |  |  |  |  |  |  |

| Others                               |                          |                    |  |  |  |  |  |  |  |

| I/F                                  | Interface                |                    |  |  |  |  |  |  |  |

| MISC                                 | Miscellaneous Interface  |                    |  |  |  |  |  |  |  |

| NC                                   | Not Connected. Reserved. |                    |  |  |  |  |  |  |  |

| Р                                    | Power Plane              |                    |  |  |  |  |  |  |  |

#### Notes:

- 1. PWR\*: The power of the pin is supplied from the **carrier board** connected to the power supply.

- 2. The Advantech's SOM-ETX boards need +5V only, so the A12, A16, A24 pins are **NC**.

- 3. Please refer to Chapter 5 for detailed descriptions.

## 3.1 Connector X1 (PCI-Bus, USB, Audio)

| Table 3.2 Connector X1 Pin Assignments |               |          |          |      |            |         |       |       |          |  |  |

|----------------------------------------|---------------|----------|----------|------|------------|---------|-------|-------|----------|--|--|

|                                        |               | <u>.</u> |          |      | <b>D</b> : | 0.      |       | 1/0   | <b>D</b> |  |  |

| Pin                                    | Signal        | I/F      | I/O      | Р    | Pin        | Signal  | I/F   | I/O   | Р        |  |  |

| A1                                     | GND           | PWR      | PWR*     | -    | A2         | GND     | PWR   | PWR*  | -        |  |  |

| A3                                     | PCICLK3       | PCI      | 0        | VCC3 | A4         | PCLCLK4 | PCI   | 0     | VCC3     |  |  |

| A5                                     | GND           | PWR      | PWR*     | -    | A6         | GND     | PWR   | PWR*  | -        |  |  |

| A7                                     | PCLCLK1       | PCI      | 0        | VCC3 | A8         | PCLCLK2 | PCI   | 0     | VCC3     |  |  |

| A9                                     | REQ3#         | PCI      |          | VCC3 | A10        | GNT3#   | PCI   | 0     | VCC3     |  |  |

| A11                                    | GNT2#         | PCI      | 0        | VCC3 | A12        | VCC3*   | -     | -     | -        |  |  |

| A13                                    | REQ2#         | PCI      | 1        | VCC3 | A14        | GNT1#   | PCI   | 0     | VCC3     |  |  |

| A15                                    | REQ1#         | PCI      |          | VCC3 | A16        | VCC3*   | -     | -     | -        |  |  |

| A17                                    | GNT0#         | PCI      | 0        | VCC3 | A18        | NC      | -     | -     | -        |  |  |

| A19                                    | VCC           | PWR      | PWR*     | -    | A20        | VCC     | PWR   | PWR*  | -        |  |  |

| A21                                    | SERIRQ        | PCI      | 10       | VCC3 | A22        | REQ0#   | PCI   | 1     | VCC3     |  |  |

| A23                                    | AD0           | PCI      | IO       | VCC3 | A24        | VCC3*   | -     | -     | -        |  |  |

| A25                                    | AD1           | PCI      | 10       | VCC3 | A26        | AD2     | PCI   | 10    | VCC3     |  |  |

| A27                                    | AD4           | PCI      | 10       | VCC3 | A28        | AD3     | PCI   | 10    | VCC3     |  |  |

| A29                                    | AD6           | PCI      | 10       | VCC3 | A30        | AD5     | PCI   | 10    | VCC3     |  |  |

| A31                                    | CBE0#         | PCI      | 10       | VCC3 | A32        | AD7     | PCI   | 10    | VCC3     |  |  |

| A33                                    | AD8           | PCI      | 10       | VCC3 | A34        | AD9     | PCI   | 10    | VCC3     |  |  |

| A35                                    | GND           | PWR      | PWR*     | -    | A36        | GND     | PWR   | PWR*  | -        |  |  |

| A37                                    | AD10          | PCI      | 10       | VCC3 | A38        | AUXAL   | Audio | 1     | VCC3     |  |  |

| A39                                    | AD11          | PCI      | 10       | VCC3 | A40        | MIC     | Audio | 1     | VCC3     |  |  |

| A41                                    | AD12          | PCI      | 10       | VCC3 | A42        | AUXAR   | Audio | 1     | VCC3     |  |  |

| A43                                    | AD13          | PCI      | 10       | VCC3 | A44        | ASVCC   | PWR   | PWR*  | VCC3     |  |  |

| A45                                    | AD14          | PCI      | 10       | VCC3 | A46        | SNDL    | Audio | 0     | VCC3     |  |  |

| A47                                    | AD15          | PCI      | 10       | VCC3 | A48        | ASGND   | PWR   | PWR*  | VCC3     |  |  |

| A49                                    | CBE1#         | PCI      | 10       | VCC3 | A50        | SNDR    | Audio | 0     | VCC3     |  |  |

| A51                                    | VCC           | PWR      | PWR*     | -    | A52        | VCC     | PWR   | PWR*  | -        |  |  |

| A53                                    | PAR           | PCI      | 10       | VCC3 | A54        | SERR#   | PCI   | IO/OD | VCC3     |  |  |

| A55                                    | GPERR#        | PCI      | 10       | VCC3 | A56        | NC      | -     | -     | -        |  |  |

| A57                                    | PME#          | PCI      | IO/OD    | VCC3 | A58        | USB2#   | USB   | 10    | VCC3     |  |  |

| A59                                    | LOCK#         | PCI      | 10       | VCC3 | A60        | DEVSEL# | PCI   | 10    | VCC3     |  |  |

| A61                                    | TRDY#         | PCI      | 10       | VCC3 | A62        | USB3#   | USB   | 10    | VCC3     |  |  |

| A63                                    | IRDY#         | PCI      | 10       | VCC3 | A64        | STOP#   | PCI   | 10    | VCC3     |  |  |

| A65                                    | FRAME#        | PCI      | 10       | VCC3 | A66        | USB2    | USB   | 10    | VCC3     |  |  |

| A67                                    | GND           | PWR      | PWR*     | -    | A68        | GND     | PWR   | PWR*  | -        |  |  |

| A69                                    | AD16          | PCI      | 10       | VCC3 | A70        | CBE2#   | PCI   | 10    | VCC3     |  |  |

| A71                                    | AD17          | PCI      | 10       | VCC3 | A72        | USB3    | USB   | 10    | VCC3     |  |  |

| A73                                    | AD19          | PCI      | 10       | VCC3 | A74        | AD18    | PCI   | 10    | VCC3     |  |  |

| A75                                    | AD20          | PCI      | 10       | VCC3 | A76        | USB0#   | USB   | 10    | VCC3     |  |  |

| A77                                    | AD22          | PCI      | 10       | VCC3 | A78        | AD21    | PCI   | 10    | VCC3     |  |  |

| A79                                    | AD23          | PCI      | IO       | VCC3 | A80        | USB1#   | USB   | 10    | VCC3     |  |  |

| A81                                    | AD24          | PCI      | IO       | VCC3 | A82        | CBE3#   | PCI   | 10    | VCC3     |  |  |

| A83                                    | VCC           | PWR      | PWR*     | -    | A84        | VCC     | PWR   | PWR*  | -        |  |  |

| A85                                    | AD25          | PCI      | IO       | VCC3 | A86        | AD26    | PCI   | 10    | VCC3     |  |  |

| A87                                    | AD28          | PCI      | IO       | VCC3 | A88        | USB0    | USB   | 10    | VCC3     |  |  |

| A89                                    | AD27          | PCI      | IO       | VCC3 | A90        | AD29    | PCI   | 10    | VCC3     |  |  |

| A91                                    | AD30          | PCI      | 10       | VCC3 | A92        | USB1    | USB   | 10    | VCC3     |  |  |

| A93                                    | PCIRST#       | PCI      | 0        | VCC3 | A94        | AD31    | PCI   | 10    | VCC3     |  |  |

| A95                                    | INTC#         | PCI      | IO/OD    | VCC3 | A96        | INTD#   | PCI   | IO/OD | VCC3     |  |  |

| A97                                    | INTA#         | PCI      | IO/OD    | VCC3 | A98        | INTB#   | PCI   | IO/OD | VCC3     |  |  |

| A99                                    | GND           | PWR      | PWR*     | -    | A100       | GND     | PWR   | PWR*  | -        |  |  |

|                                        | <u>  -··-</u> |          | <u> </u> | I    |            |         |       |       | l        |  |  |

VCC3\*: Output pin and only current limit 500mA.

|         | CN2A        | 독,         |             |      |

|---------|-------------|------------|-------------|------|

|         | /           | N          |             |      |

| A1      |             | ÷.         |             | A2   |

| A3      | GND_1       | Q'         | GND_6       | A4   |

| A5      | PCICLK3_PCI | $\sim$     | PCI_PCICLK4 | A6   |

| A7      | GND_2       |            | GND_7       | A8   |

| Ala     | PCICLK1_PCI | $\sim$     | PCI_PCICLK2 | -A10 |

| AII     | REQ#3_PCI   |            | PCI_GNT#3   | A12  |

| A13     | GNT#2_PCI   |            | VCC3_1      | A14  |

| A15     | REQ#2_PCI   |            | PCI_GNT#1   | A16  |

| AIZ     | REQ#1_PCI   |            | VCC3_2      | A18  |

| A19     | GNT#0_PCI   |            | NC_1        | A20  |

| A21     | VCC_1       |            | VCC_4       | A22  |

| A23     | SERIRQ      |            | PCI_REQ#0   | A24  |

| A25     | AD0_PCI     |            | VCC3_3      | A26  |

| A27     | AD1_PCI     |            | PCI_AD2     | A28  |

| A29     | AD4_PCI     |            | PCI_AD3     | A30  |

| A31     | AD6_PCI     |            | PCI_AD5     | A32  |

| A33     | CBE#0_PCI   |            | PCI_AD7     | A34  |

| A35     | AD8_PCI     |            | PCI_AD9     | A36  |

| A37     | GND_3       |            | GND_8       | A38  |

| A39     | AD10_PCI    |            | AUDIO_AUXAL | A40  |

| A41     | AD11_PCI    |            | AUDIO_MIC   | A42  |

| A43     | AD12_PCI    |            | AUDIO_AUXAR | A44  |

| A45     | AD13_PCI    |            | AUDIO_ASVCC | A46  |

| A47     | AD14_PCI    |            | AUDIO_SNDL  | A48  |

| A49     | AD15_PCI    |            | AUDIO_ASGND | A50  |

| A51     | CBE#1_PCI   |            | AUDIO_SNDR  | A52  |

| A53     | VCC_2       |            | VCC_5       | A54  |

| A55     | PAR_PCI     |            | PCI_SERR#   | A56  |

| A57.4   | GPERR#_PCI  |            | NC_2        | A58  |

| A59     | PME#_PCI    |            | USB_USB2-   | -A60 |

| A61     | LOCK#_PCI   |            | PCI_DEVSEL# | A62  |

| A63     | TRDY#_PCI   |            | USB_USB3-   | A64  |

| A65_    | IRDY#_PCI   |            | PCI_STOP#   | A66  |

| A67     | FRAME#_PCI  |            | USB_USB2+   | A68  |

| A69     | GND_4       |            | GND         | A70  |

| A71     | AD16_PCI    |            | PCI_CBE#2   | A72  |

| A73     | AD17_PCI    |            | USB_USB3+   | A74  |

| A75     | AD19_PCI    |            | PCI_AD18    | A76  |

| A77     | AD20_PCI    |            | USB_USB0-   | A78  |

| A79     | AD22_PCI    |            | PCI_AD21    | A80  |

| A81     | AD23_PCI    |            | USB_USB1-   | A82  |

| A83     | AD24_PCI    |            | PCI_CBE#3   | A84  |

| A85     | VCC_3       |            | VCC_6       | A86  |

| A87     | AD25_PCI    |            | PCI_AD26    | A88  |

| A89     | AD28_PCI    |            | USB_USB0+   | A90  |

| A91     | AD27_PCI    |            | PCI_AD29    | A92  |

| A93     | AD30_PCI    | ~          | USB_USB1+   | A94  |

| A95     | PCIRST#_PCI | 0          | PCI_AD31    | -A96 |

| A97     | INTC#_IRQY  | -          | INTD#_IRQZ  | RA98 |

| A99     | INTA#_IRQW  | <u>e</u> . | INTB#_IRQX  | A100 |

| <u></u> | GND_5       | NC_13      | GND10       |      |

|         |             | ž          |             |      |

|         | ETX-PC-1    | _          |             |      |

|         |             |            |             |      |

## Connector X1 (PCI-Bus, USB, Audio) Schemaitc

## 3.2 Connector X2 (ISA-Bus)

| Table 3.3 Connector X2 Pin Assignments |         |     |      |        |      |         |     |      |        |  |  |  |

|----------------------------------------|---------|-----|------|--------|------|---------|-----|------|--------|--|--|--|

|                                        |         |     | U    | P      | Dim  | Circul  | 1/5 | 1/0  | В      |  |  |  |

| Pin                                    | Signal  |     |      | F      | Pin  | Signal  |     |      | Р      |  |  |  |

| B1                                     | GND     | PWR | PWR* | -      | B2   | GND     | PWR | PWR* | -      |  |  |  |

| B3                                     | SD14    | ISA | 10   | VCC3/5 | B4   | SD15    | ISA | 10   | VCC3/5 |  |  |  |

| B5                                     | SD13    | ISA | 10   | VCC3/5 | B6   | MASTER# | ISA |      | VCC3/5 |  |  |  |

| B7                                     | SD12    | ISA | 10   | VCC3/5 | B8   | DREQ7   | ISA |      | VCC3/5 |  |  |  |

| B9                                     | SD11    | ISA | 10   | VCC3/5 | B10  | DACK7#  | ISA | 0    | VCC3/5 |  |  |  |

| B11                                    | SD10    | ISA | 10   | VCC3/5 | B12  | DREQ6   | ISA |      | VCC3/5 |  |  |  |

| B13                                    | SD9     | ISA | 10   | VCC3/5 | B14  | DACK6#  | ISA | 0    | VCC3/5 |  |  |  |

| B15                                    | SD8     | ISA | 10   | VCC3/5 | B16  | DREQ5   | ISA |      | VCC3/5 |  |  |  |

| B17                                    | MEMW#   | ISA | 10   | VCC3/5 | B18  | DACK5#  | ISA | 0    | VCC3/5 |  |  |  |

| B19                                    | MEMR#   | ISA | 0    | -      | B20  | DREQ0   | ISA |      | -      |  |  |  |

| B21                                    | LA17    | ISA | 10   | VCC3/5 | B22  | DACK0#  | ISA | 0    | VCC3/5 |  |  |  |

| B23                                    | LA18    | ISA | 10   | VCC3/5 | B24  | IRQ14   | ISA |      | VCC3/5 |  |  |  |

| B25                                    | LA19    | ISA | 10   | VCC3/5 | B26  | IRQ15   | ISA |      | VCC3/5 |  |  |  |

| B27                                    | LA20    | ISA | 10   | VCC3/5 | B28  | IRQ12   | ISA |      | VCC3/5 |  |  |  |

| B29                                    | LA21    | ISA | 10   | VCC3/5 | B30  | IRQ11   | ISA |      | VCC3/5 |  |  |  |

| B31                                    | LA22    | ISA | 10   | VCC3/5 | B32  | IRQ10   | ISA | 1    | VCC3/5 |  |  |  |

| B33                                    | LA23    | ISA | Ю    | VCC3/5 | B34  | IO16#   | ISA | 1    | VCC3/5 |  |  |  |

| B35                                    | GND     | PWR | PWR* | -      | B36  | GND     | PWR | PWR* | -      |  |  |  |

| B37                                    | SBHE#   | ISA | 10   | VCC3/5 | B38  | M16#    | ISA | 10   | VCC3/5 |  |  |  |

| B39                                    | SA0     | ISA | IO   | VCC3/5 | B40  | OSC     | ISA | 0    | VCC3/5 |  |  |  |

| B41                                    | SA1     | ISA | IO   | VCC3/5 | B42  | BALE    | ISA | 0    | VCC3/5 |  |  |  |

| B43                                    | SA2     | ISA | 10   | VCC3/5 | B44  | TC      | ISA | 0    | VCC3/5 |  |  |  |

| B45                                    | SA3     | ISA | 10   | VCC3/5 | B46  | DACK2#  | ISA | 0    | VCC3/5 |  |  |  |

| B47                                    | SA4     | ISA | 10   | VCC3/5 | B48  | IRQ3    | ISA | 1    | VCC3/5 |  |  |  |

| B49                                    | SA5     | ISA | 10   | VCC3/5 | B50  | IRQ4    | ISA | 1    | VCC3/5 |  |  |  |

| B51                                    | VCC     | PWR | PWR* | -      | B52  | VCC     | PWR | PWR* | -      |  |  |  |

| B53                                    | SA6     | ISA | 10   | VCC3/5 | B54  | IRQ5    | ISA | Ι    | VCC3/5 |  |  |  |

| B55                                    | SA7     | ISA | 10   | VCC3/5 | B56  | IRQ6    | ISA | 1    | VCC3/5 |  |  |  |

| B57                                    | SA8     | ISA | 10   | VCC3/5 | B58  | IRQ7    | ISA | 1    | VCC3/5 |  |  |  |

| B59                                    | SA9     | ISA | 10   | VCC3/5 | B60  | SYSCLK  | ISA | 0    | VCC3/5 |  |  |  |

| B61                                    | SA10    | ISA | 10   | VCC3/5 | B62  | REFSH#  | ISA | 10   | VCC3/5 |  |  |  |

| B63                                    | SA11    | ISA | 10   | VCC3/5 | B64  | DREQ1   | ISA | 1    | VCC3/5 |  |  |  |

| B65                                    | SA12    | ISA | 10   | VCC3/5 | B66  | DACK1#  | ISA | 0    | VCC3/5 |  |  |  |

| B67                                    | GND     | PWR | PWR* | -      | B68  | GND     | PWR | PWR* | -      |  |  |  |

| B69                                    | SA13    | ISA | 10   | VCC3/5 | B70  | DREQ3   | ISA | 1    | VCC3/5 |  |  |  |

| B71                                    | SA14    | ISA | 10   | VCC3/5 | B72  | DACK3#  | ISA | 0    | VCC3/5 |  |  |  |

| B73                                    | SA15    | ISA | 10   | VCC3/5 | B74  | IOR#    | ISA | 10   | VCC3/5 |  |  |  |

| B75                                    | SA16    | ISA | 10   | VCC3/5 | B76  | IOW#    | ISA | 10   | VCC3/5 |  |  |  |

| B77                                    | SA18    | ISA | 10   | VCC3/5 | B78  | SA17    | ISA | 10   | VCC3/5 |  |  |  |

| B79                                    | SA19    | ISA | 10   | VCC3/5 | B80  | SMEMR#  | ISA | 0    | VCC3/5 |  |  |  |

| B81                                    | IOCHRDY | ISA | 10   | VCC3/5 | B82  | AEN     | ISA | 0    | VCC3/5 |  |  |  |

| B83                                    | VCC     | PWR | PWR* | -      | B84  | VCC     | PWR | PWR* | -      |  |  |  |

| B85                                    | SD0     | ISA | IO   | VCC3/5 | B86  | SMEMW#  | ISA | 10   | VCC3/5 |  |  |  |

| B87                                    | SD2     | ISA | IO   | VCC3/5 | B88  | SD1     | ISA | 10   | VCC3/5 |  |  |  |

| B89                                    | SD3     | ISA | 10   | VCC3/5 | B90  | NOWS#   | ISA | Ι    | VCC3/5 |  |  |  |

| B91                                    | DREQ2   | ISA |      | VCC3/5 | B92  | SD4     | ISA | 10   | VCC3/5 |  |  |  |

| B93                                    | SD5     | ISA | Ю    | VCC3/5 | B94  | IRQ9    | ISA | 1    | VCC3/5 |  |  |  |

| B95                                    | SD6     | ISA | 10   | VCC3/5 | B96  | SD7     | ISA | 10   | VCC3/5 |  |  |  |

| B97                                    | IOCHK#  | ISA | 1    | VCC3/5 | B98  | RSTDRV  | ISA | 0    | VCC3/5 |  |  |  |

| B99                                    | GND     | PWR | PWR* | -      | B100 | GND     | PWR | PWR* | -      |  |  |  |

|                                        |         |     |      | l      |      | =       |     |      | L      |  |  |  |

|            | ector X2 (ISA-Bus                 | s) Schematic |             |             |

|------------|-----------------------------------|--------------|-------------|-------------|

|            | CN2B                              |              |             |             |

|            |                                   | 4            |             |             |

| B1         | GND 11                            |              | GND 15      | B2          |

| B3         | SD14 ISA                          | ~ ž          | ISA SD15    | B4          |

| B5         | SD14_ISA                          | $-C\Sigma$   | ISA MASTER# | 0 <u>B6</u> |

| B7         | SD12_ISA                          | $\cup$       | ISA DREQ7   | B8          |

| <b>B</b> 9 | SD12_ISA                          |              | ISA DACK#7  | <u>B10</u>  |

| B11        | SD10_ISA                          |              | ISA DREQ6   | B12         |

| B13        | SD9 ISA                           |              | ISA DACK#8  | <u>B14</u>  |

| B15        | SD8_ISA                           |              | ISA DREQ5   | B16         |

| B17        | MEMW# ISA                         |              | ISA DACK#5  | <u>B18</u>  |

| B19        | MEMR# ISA                         |              | ISA DREQ0   | B20         |

| B21        | LA17 ISA                          |              | ISA DACK#0  | 0B22        |

| B23        | LA18 ISA                          |              | ISA IRQ14   | B24         |

| B25        | LA19 ISA                          |              | ISA IRQ15   | B26         |

| B27        | LA20 ISA                          |              | ISA IRQ12   | B28         |

| B29        | LA21 ISA                          |              | ISA IRQ11   | B30         |

| B31        |                                   |              |             | B32         |

| B33        | LA22_ISA                          |              | ISA_IRQ10   | ~B34        |

| B35        | LA23_ISA                          |              | ISA_I016#   | B36         |

| B37        | GND_12                            |              | GND_16      | -B38        |

| B39        | SBHE#_ISA                         |              | ISA_M16#    | B40         |

| B41        | SA0_ISA                           |              | ISA_OSC     | B42         |

| B43        | SA1_ISA                           |              | ISA_BALE    | B44         |

| B45        | SA2_ISA                           |              | ISA_TC      | -B46        |

| B47        | SA3_ISA                           |              | ISA_DACK#2  | B48         |